问题列表(整理中):

1. 如何定义信号量数组

如果cpld里想用信号量数组,并使每个元素对应到不同PIN,可以在ve里定义如下:

- mcu_a[0] PIN_31

- mcu_a[1] PIN_32

- mcu_a[2] PIN_33

- mcu_a[3] PIN_34

- ...

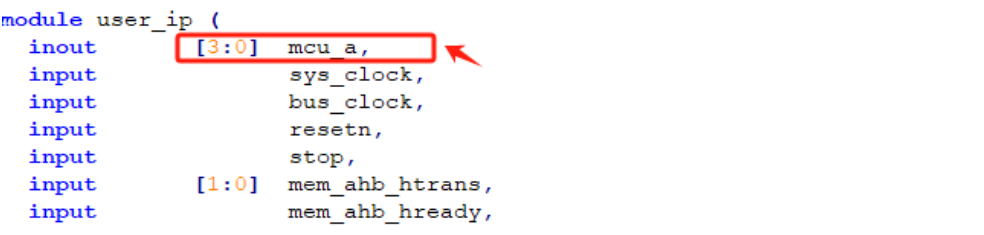

如图:

那么,prepare LOGIC后,将在自动生成的cpld框架.v接口里,表示如下:

这里就表现为数组的形式了。

.

2. 在cpld输出相位差90度的时钟

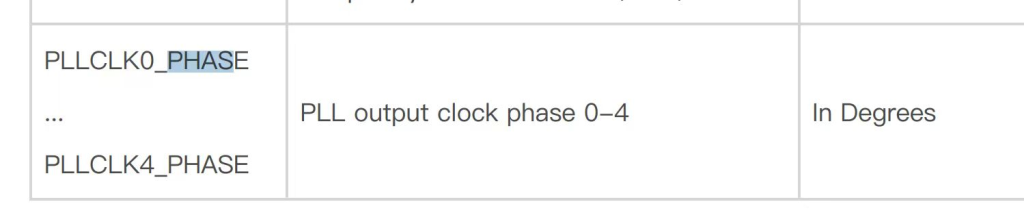

可以在ve里(使用PHASE字段)定义如下:

具体使用如下图:

在上图的定义中,就是把pllclk4的输出,在相位上偏移90度。

除了90度,还可以输出180度和270度。

.

3. 更换了芯片怎么设置工程

比如,原先使用的是100Pin的flash大小是1M的,现在要更换成64Pin的flash是256K的。(其他的更换也是相似)

那么需要修改的点:

- 在platformio.ini里修改 board 字段类型,如果是1M的flash就选 agrv2k_407,如果是256k就选 agrv2k_303(还有个103,和303是完全一样的);

- 继续在platformio.ini里修改 logic_device 字段类型,根据实际使用的,选择一个(可选:AGRV2KL100 / AGRV2KL64 / AGRV2KL64H / AGRV2KL48 / AGRV2KQ32);

- 在.ve文件里,按新的管脚一一配置好;(注意:不要留无效的配置。无效的都注释掉或删除掉)

如果没有使用自定义logic,那么以上3步配置完就可以了。烧录logic、烧录code就能正常运行了。

如果使用了自定义logic,那么logic部分需要从头做一遍:

- 先把工程下logic目录改名(相当于备份下);

- 在vscode里重新 prepare LOGIC,生成出来新的cpld空工程;

- 启动quartus,打开该新工程运行tcl script脚本;

- 把前边的逻辑(第1步改名的那个)移到新的logic下,重新编译;

- 再重新用supra打开该工程编译;

- 再回到VSCode下upload LOGIC,把新的logic.bin烧录到板子上。

如果logic制作流程有忘记的,请回到这里查看细节。

.